ASIC

ASIC, קיצור של מעגל משולב תלוי יישום (Application Specific Integrated Circuit) הוא מעגל משולב או שבב התפור ליישום ייחודי ומסוים להבדיל ממעגלים משולבים תקניים לשימוש כללי. שבב שנבנה במיוחד ליישום של טלפון סלולרי מסוים, למשל, הוא ASIC. ההבדל בין שבב תקני כמוצר מדף הקרוי גם ASSP הוא בעיקר במשך זמן ומתודולוגיית התכנון ופחות בתהליך הייצור.

ככל שגדלי השבבים התכווצו וכלי התכנון השתפרו במהלך השנים, הסיבוכיות והפונקציונליות הביאו לצמיחת ממדי ה-ASIC מ-5,000 בשנות ה-80 ועד ליותר מ-100 מיליון שערים לוגיים.

ASIC מודרניים כוללים ליבות שלמות של מעבדים, DSP, מבני זיכרון כמו ROM, RAM, EEPROM, Flash, מכלולים אנלוגיים ומעורבים Mixed Signal, מכלולי תדר רדיו ואבני בניין גדולות אחרות.

ASIC אלו מכונים מערכת-על-שבב או SoC - System On a Chip. מתכנני ASIC מתארים ומקודדים את תכנון השבב על ידי שימוש בשפות לתיאור חומרה כמו Verilog ו-VHDL, מאמתים את התכנון על ידי שימוש בכלים אוטומטיים ממוחשבים (EDA) ומממשים אותו. FPGA לעיתים היא אלטרנטיבה לפיתוח ASIC כאשר מדובר באילוצי זמן קצרים לפיתוח השבב, כאשר כמויות הייצור הן נמוכות וכאשר יש צורך באב טיפוס. ל-ASIC לעומת FPGA יש עלויות חד פעמיות גבוהות הנקראות NRE - Non Recurring Engineering היכולות להגיע למיליוני דולרים.

היסטוריה

ה-ASIC הראשון פותח בשנות ה-80 על ידי חברת פרנטי והיה מבוסס על ארכיטקטורה הנקראת Gate Array - מערך שערים. השימוש המסחרי היה על ידי חברת סינקלייר עם מחשבי ה-Z80.

תכנון תאים תקניים

בשנות ה-80 המתכננים נדרשו לבחור יצרן ASIC ולהשתמש בכלי התכנון שהציע היצרן. למרות שכלי פיתוח מחברות חיצוניות אחרות היו זמינים, הקישור בין כלי הפיתוח והספריות של היצרן לא היה יעיל. ובסופו של דבר נדרשו המתכננים להשתמש בכלי הפיתוח של היצרנים. פתרון לבעיה זו שגם הניב שיפור בתוצאות ובהגדלת יכולת המזעור של ASIC הוא מימוש ארכיטקטורה הנקראת תא סטנדרטי או "Standart Cell". בשיטה זו כל יצרן ASIC יצר בלוקים פונקציונליים עם תכונות ומאפיינים אלקטרוניים ידועים מראש כמו זמני השהיה, השראות וקיבוליות.

תכנון בשיטת מערכי שערים

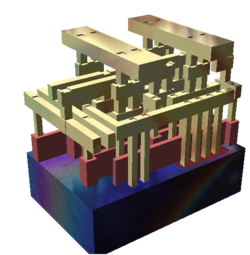

תכנון בשיטת מערכי שערים הוא שיטת ייצור בה שכבות הדיפוזיה של הטרנזיסטורים (ללא החיבורים) מוכנות מראש וממתינות באחסנה לשלב האחרון של החיבוריות הממומשת על ידי שכבות מתכתיות, כ-2 - 5 שכבות ברוב טכנולוגיות ה-ASIC. בכך ניתן לקצר בצורה משמעותית את זמן הייצור ואת עלויות ה-NRE הגבוהות. המתכנן נדרש למפות את ה-ASIC בפיתוח אל מערכי התאים ולהגיע לאופטימיזציה של ניתוב ומיקום (Place & Route) החיבורים שאף פעם לא מגיע ל-100% ניצול של השערים הקיימים מבעוד מועד על פיסת הסיליקון.

מערך שערים טהור של לוגיקה בלבד כבר אינו נמצא בשימוש היום והוחלף על ידי טכנולוגיית ה-FPGA. כיום מערכי שערים התפתחו ל-ASIC מבני המכיל ליבות גדולות של תכנונים (IP - Intelectual Property) כמו CPU, DSP וזיכרונות לצד בלוקים של מערכי שערים המוכנים להגדרה כחלק מהארכיטקטורה של מערכת-על-שבב. שיטה זו גם נקראת תכנון מלא למחצה (Semi Custom).

תכנון מלא

תכנון מלא (Full Custom) הוא פיתוח ותכנון של ASIC בכל שלבי הייצור ובכל שכבות הפוטוליתוגרפיה של התקן כלשהו ומשמש גם בפיתוח ASIC וגם במוצרי מדף תקניים המיוצרים ונמכרים בכמויות גדולות על ידי חברות ויצרני שבבים כדוגמת אינטל. חברות קטנות יותר כמו חברות הזנק שלהם אין יכולות ייצור (Fabrication) נקראות לעיתים Fabless והן לרוב הלקוחות העיקריים של יצרני ונותני שירות בתחום שוק ה-ASIC.

לתכנון מלא ישנם יתרונות רבים בהוזלת הייצור ועלות הרכיבים, הקטנת וניצול מקסימליים של שטח השבב, שיפור הביצועים, הורדת צריכת ההספק ויכולת לשלב מרכיבים אנלוגיים ובלוקים שיוצרו קודם לכן (אשר אומתו ונבדקו).

תכנון מבני

תכנון מבני או תכנון פלטפורמי הוא תכנון הקרוב ל-ASIC בו נקבעים מראש חלק משכבות המתכת (החיבוריות) והשכבות הלוגיות כך שניתן להקטין עוד יותר את זמן ועלות התכנון ובכך מתקרב יותר ל-FPGA. בתכנון זה ניתן לשלב ליבות קיימות והוא הרחבה של תכנון מערכי שערים בו מוזילים עוד יותר את עלות ייצור השכבות.

ספריות תאים וליבות

ספריות תאים הם תיאור ותכונות של בלוקים ורכיבים (הכוללים מעגלים, שערים וטרנזיסטורים) המוגדרים מראש על ידי היצרן ומסופקים על ידו. אספקתם איננה כרוכה בעלות נוספת על ידי היצרן אך המידע הנמסר תחתן נשמר חסוי. הגדרתם מראש במלואה נקרא גם Hard Macro.

ליבות IP או קניין רוחני הם תכנונים הנרכשים על ידי ספקי "צד ג'" כתת-רכיב כחלק מ-ASIC גדול יותר. הם מסופקים בצורת קוד בשפת תיאור חומרה (Soft Macro) או כתכנון מלא הכולל את ניתובי החיבורים בטכנולוגיית היצרן כליבה סגורה ומוגנת וניתנת לייצור ישיר של המסיכות (Hard Macro). קיימות חברות רבות המפתחות ומוכרות ליבות IP, ובחברות גדולות קיימות מחלקות שזהו תפקידם. ניתן לרכוש למשל תכנון שלם של CPU, בקר Ethernet, USB או מכלול Wi-Fi שלם שאותם ניתן לשבץ לתוך ASIC.

יצרני ASIC

ראו גם

לקריאה נוספת

- Kevin Morris (2003-11-23). "Cost-Reduction Quagmire: Structured ASIC and Other Options". FPGA and Programmable Logic Journal. אורכב מ-המקור ב-2006-05-15. נבדק ב-2009-05-13.

- Jim Turley (2005-04-07). "Hard Choices Among FPGA Hardening Options". TechOnline.(הקישור אינו פעיל)

- Anthony Cataldo (2002-03-26). "Xilinx looks to ease path to custom FPGAs". EE Times. CMP Media, LLC.

- "Xilinx intros next-gen EasyPath FPGAs priced below structured ASICs". EDP Weekly's IT Monitor. Millin Publishing, Inc. 2004-10-18.

- Golshan, K. (2007). Physical design essentials: an ASIC design implementation perspective. New York: Springer. מסת"ב 0-387-36642-3.

קישורים חיצוניים

- מדריך ASIC למתחילים (באנגלית)

ASIC33227328Q217302