Clock Gating

קטימת שעון (באנגלית: Clock gating) היא טכניקה פופולרית לחיסכון בהספק של שבבים. בשיטה זו חלקים שונים בשבב מושבתים, כאשר אינם בשימוש, ולכן לא מתבזבז עליהם הספק.

לדוגמה: כאשר לשבב יש ממשקי כניסת ויציאת מידע של PCI, Ethernet ו-USB אבל בפועל במעגל שבו השבב משולב הוא משתמש רק בממשק ה-USB אין צורך שמעגלי הממשקים האחרים יעבדו וניתן לכבות אותם.

פרטים

רקע

במעגל משולב אשר מכיל מעגלים סינכרוניים מחולק בתוכו לתתי יחידות ארגונית (מודולים) כאשר בדרך כלל יש תמיכה ומשאבי חומרה המאפשרים שימוש נרחב ביכולות המעגל, כך שנוצר מצב שברוב תצורות ההפעלה של המעגל אין דורש להשתמש בכל חלקיו.

במעגלים סינכרוניים מתבצעים חישובים אשר הקלט והפלט שלהם מגיע ונשמר בתאי זיכרון. במהלך העבודה התקינה של המעגל מתבצע מיתוג חשמלי בין המצבים הלוגיים "0" ו "1", כאשר במהלך פעולת המיתוג של המעגל מתבזבז הספק חשמל.

תאי הזיכרון במעגלים הללו מופעלים על ידי אות שעון ובלעדיו המעגלים הללו אינם פעילים.

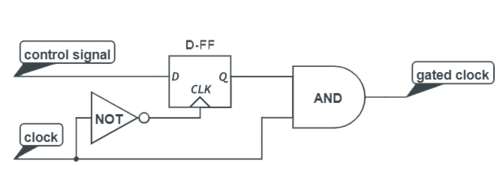

השיטה

בשיטה זו נוסף מעגל חשמלי (Clock Gate) אשר קוטם את התפשטות אות השעון במערכת (Clock tree) עבור חלקים במעגל שאנחנו רוצים לאפשר את כיבויים. מעגל זה מקבל אות בקרה אשר לפיו הוא מאפשר לאות השעון להיכנס לחלק במעגל שעליו הוא מפקח. אם אות הבקרה מורה לו לכבות את החלק המפוקח אז המעגל יוציא "0" לוגי קבוע לתוך כניסת השעון של החלק המפוקח. אחרת, יעבור אות השעון ישירות לתוך המעגל המפוקח בצורה תקינה (עם עיכוב קטן).

קטימת אות השעון משביתה חלק של המעגל החשמלי, וכך הדלגלגים שלו לא מחליפים מצבים לוגיים, אינם מבצעים פעולת מיתוג, ולכן צריכת ההספק במעגל המפוקח יורדת לאפס, וההספק מתבזבז בצורה זניחה רק עקב התהוות של זרמי זליגה.

מימוש

קיימים תאי ספרייה מובנים עבור טכנולוגיות שונות של בניית שבבים שתפקידם הוא ליצור מעגל קוטם שעון מתאים. הם נקראים Integrated clock gating (ICG) cells.

ניתן להוסיף למעגל Clock Gate במספר דרכים:

- באמצעות קידוד לשפת תיאור החומרה (RTL/HDL) הוראה המאפשרת לכלי הסינתזה ליצור מעגל קוטם שעון, בדרך כלל הוספת תנאי על אות השעון.

- באמצעות הוספת מופע של תא ספרייה מתאים (ICG cell) לתוך ה־RTL, בדרך כלל על אות השעון בכניסה למודולים שאותם מעוניינים להוסיף להם את מנגנון הכיבוי.

- באמצעות הוספה חצי אוטומטית על ידי כלי הסינתזה - כלי הסינתזה מבצע אופטימיזציה ומוסיף לבד או מציע להוסיף לתוך ה־RTL תנאי אפשור לשעון או הצבת מופעים של ICG cells. במקביל כלי הסינתזה מבצע את ההתאמות הנדרשות לעבודה תקינה של עץ השעון.

דוגמאות למימוש

- קטע הקוד הבא בשפת verilog מסמן לכלי הסינתזה לבנות תא זיכרון D ובכניסת אות השעון שלו להציב Clock gate.

הקוד מתאר מעגל ובו תא זיכרון עם כניסה d, יציאה q, אות אתחול rst_n, אות שעון clk ובנוסף ואות בקרה enable המפעיל את מעגל ה clock gate. אות השעון נכנס למעגל ה־clock gate ולאחר מכן נכנס לכניסת השעון של תא הזיכרון.

always @(posedge clk or negedge rst_n)

begin

if (!rst_n)

q <= 1'b0 ;

else if(enable)

q <= d ;

end

השפעת הקטימה על אות השעון

- במהלך תכנון הוספת מעגלי קטימת שעון יש להתחשב בצורה ייחודית בבניית העץ של אות השעון. יש לקחת בחשבון גם עיכובים הנוצרים באות השעון בחלק מהמעגלים בהם יש את מעגלי קטימת השעון, ללא התחשבות בתנאים הללו הוספת מעגלי קטימת השעון עלולה להזיק לעץ ולכן תגרום יותר נזק מתועלת.

- שעון קטום עוקב הוא תהליך של חילוץ / הפצת התנאים המאפשרים למעגלים עוקבים במעלה או במורד אות השעון המתפשט, כך שמעגלים ותאי זיכרון נוספים יקטמו על ידי השעון.

- אף על פי שמעגלים אסינכרוניים מעצם הגדרתם אינם כוללים אות שעון, המונח "אות שעון קטום מושלם" משמש להמחשת האופן שבו טכניקות קטימת השעון השונות הן פשוט קירובים של ההתנהגות העברת מידע המוצגת על ידי מעגל אסינכרוני. ככל שאופן קטימתו של המעגל הסינכרוני מתקרב לאפס, צריכת ההספק של המעגל הזה מתקרבת למעגל אסינכרוני והמעגל מייצר מעברים לוגיים רק כאשר הוא פעיל.

יתרונות

- יתרונה הגדול של השיטה היא חיסכון בהספק חשמלי דבר אשר גורר צריכת אנרגיה נמוכה יותר של השבב. צריכת אנרגיה נמוכה יותר מאפשרת ליצרן להשתמש בסוללה קטנה יותר או לאפשר משך חיים ארוך יותר.

- חיסכון בהספק תורם לכך שפיזור החום הנדרש מהשבב נמוך יותר ולכן דרישות הקירור נמוכות יותר לרכיב כולו.

- במקרים רבים הוספת מעגלי Clock Gate מחליפה שימוש במרבב וכך חוסכת שטח רב והספק במעגל (במעגל המכיל מרבב כניסת המרבב יכולה להגיע למספר מעגלי המשך, לעומת מעגל המכיל Clock Gate אשר בו המידע מפוצל ישירות לכל מעגלי ההמשך ורק המעגלים הרלוונטיים דלוקים)[1].

חסרונות

- הוספת סיבוכיות ל"עץ השעון" (Clock Tree) - הוספת מעגלים ולוגיקה לעץ השעון עלולה לשנות את מבנה העץ וליצור עיכובים בהגעת השעון לחלק מרכיבי המעגל כך שפעולתו הסינכרונית תיפגע והוא יפסיק לעבוד בצורה תקינה.

- הוספת מעגל זה מוסיפה מעט לוגיקה למעגל ומגדילה את השטח הנדרש למימושו.

שימושים

בשבבים המתוכננים לעבודה עם סוללות או הספק עבודה נמוך, כגון אלה המשמשים את הטלפונים הניידים, התקנים לבישים, חיישנים וכו' משתמשים במספר צורות של קטימת שעון יחדיו. מצד אחד נשלטים מעגלי קטימת השעון על ידיד אותות הבקרה של התוכנה המנהלת את השבב, כאשר מנהל ההתקן מאפשר או משבית את השעון במקומות המתאימים. בצד השני קיים מנגנון שליטה אוטומטי של הלוגיקה החומרתית בו היא מזהה האם יש עבודה לעשות, ומכבה את השעון הרלוונטי עבור מודול שאינו נחוץ.

צורות אלה מקיימות אינטראקציה זו עם זו ועשויות להיות חלק מאותו עץ שעון. לדוגמה, עבור גשר פנימי (internal bridge) או ערוץ העברת סיגנלים רחב (bus) עשויים להשתמש בקטימת שעון אוטומטית כך שהוא ייכבה עד שהמעבד או מנוע DMA צריכים להשתמש בו, בעוד שחלק מהציוד ההיקפי בערוץ העברת סיגנלים רחב זה עלול להיקטם לצמיתות אם הוא אינו בשימוש עבור אותו לוח.

ראו גם

לקריאה נוספת

- "Deterministic clock gating for microprocessor power reduction". The Ninth International Symposium on High-Performance Computer Architecture, 2003. HPCA-9 2003. Proceedings. IEEE. 2003-02-28 [2003-02-12]. doi:10.1109/HPCA.2003.1183529. ISBN 0-7695-1871-0. ISSN 1530-0897. ארכיון מ-2018-07-09. נבדק ב-2018-07-09.

- Margaret Rouse, Definition Clock gating, https://whatis.techtarget.com, פברואר 2016 (באנגלית)

- yed Shakir Iqbal, Nishant Madan, Mayank Tutwani (Freescale Semiconductors India Pvt. Ltd), Low Power High Density Clock Gate, https://www.design-reuse.com (באנגלית)

הערות שוליים

- ↑ Cadence Design Systems, Clock Gating Dynamic power reduction by gating the clock, https://www.design-reuse.com, 18 באפריל 2017 (באנגלית)

שגיאות פרמטריות בתבנית:מיון ויקיפדיה

שימוש בפרמטרים מיושנים [ דרגה ] Clock Gating28446965